This morning the PCI Particular Curiosity Group (PCI-SIG) is releasing the much-awaited last (1.0) specification for PCI Categorical 6.0. The following era of the ever present bus is as soon as once more doubling the information fee of a PCIe lane, bringing it to 8GB/second in every course – and much, far increased for multi-lane configurations. With the ultimate model of the specification now sorted and authorised, the group expects the primary industrial {hardware} to hit the market in 12-18 months, which in observe means it ought to begin exhibiting up in servers in 2023.

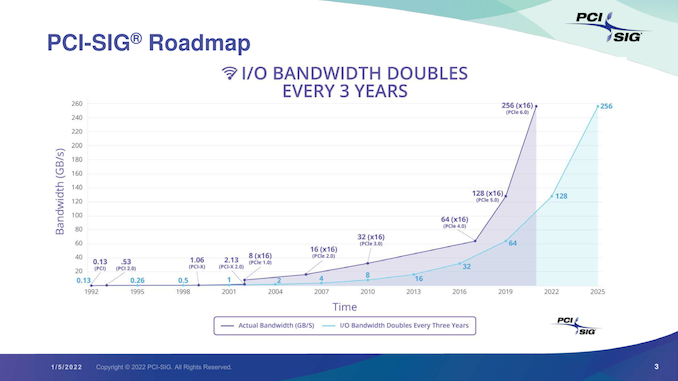

First introduced in the summertime of 2019, PCI Categorical 6.0 is, because the identify implies, the quick follow-up to the current-generation PCIe 5.0 specification. Having made it their purpose to maintain doubling PCIe bandwidth roughly each 3 years, the PCI-SIG virtually instantly set about work on PCIe 6.0 as soon as the 5.0 specification was accomplished, taking a look at methods to as soon as once more double the bandwidth of PCIe. The product of these growth efforts is the brand new PCIe 6.0 spec, and whereas the group has missed their unique purpose of a late 2021 launch by mere weeks, at the moment they’re saying that the specification has been finalized and is being launched to the group’s members.

As at all times, the creation of a good quicker model of PCIe know-how has been pushed by the insatiable bandwidth wants of the business. The quantity of knowledge being moved by graphics playing cards, accelerators, community playing cards, SSDs, and different PCIe gadgets solely continues to extend, and thus so should bus speeds to maintain these gadgets fed. As with previous variations of the usual, the quick demand for the quicker specification comes from server operators, whom are already repeatedly utilizing giant quantities of high-speed {hardware}. However in due time the know-how ought to filter right down to client gadgets (i.e. PCs) as nicely.

By doubling the pace of a PCIe hyperlink, PCIe 6.0 is an across-the-board doubling of bandwidth charges. X1 hyperlinks transfer from 4GB/second/course to 8GB/second/course, and that scales all the way in which as much as 128GB/second/course for a full x16 hyperlink. For gadgets which are already suturing a hyperlink of a given width, the additional bandwidth represents a major improve in bus limits; in the meantime for gadgets that aren’t but saturating a hyperlink, PCIe 6.0 presents a chance to scale back the width of a hyperlink, sustaining the identical bandwidth whereas bringing down {hardware} prices.

| PCI Categorical Bandwidth (Full Duplex: GB/second/course) |

||||||||

| Slot Width | PCIe 1.0 (2003) |

PCIe 2.0 (2007) |

PCIe 3.0 (2010) |

PCIe 4.0 (2017) |

PCIe 5.0 (2019) |

PCIe 6.0 (2022) |

||

| x1 | 0.25GB/sec | 0.5GB/sec | ~1GB/sec | ~2GB/sec | ~4GB/sec | 8GB/sec | ||

| x2 | 0.5GB/sec | 1GB/sec | ~2GB/sec | ~4GB/sec | ~8GB/sec | 16GB/sec | ||

| x4 | 1GB/sec | 2GB/sec | ~4GB/sec | ~8GB/sec | ~16GB/sec | 32GB/sec | ||

| x8 | 2GB/sec | 4GB/sec | ~8GB/sec | ~16GB/sec | ~32GB/sec | 64GB/sec | ||

| x16 | 4GB/sec | 8GB/sec | ~16GB/sec | ~32GB/sec | ~64GB/sec | 128GB/sec | ||

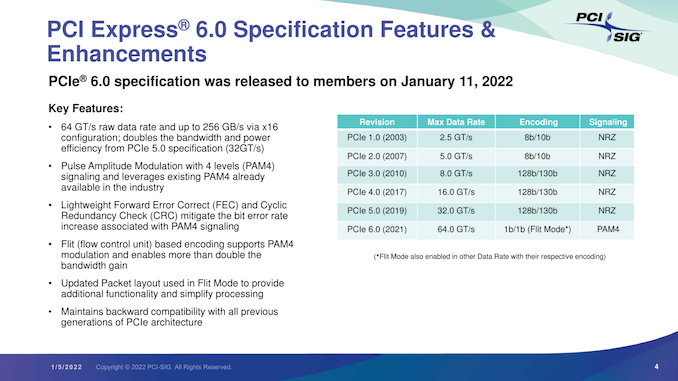

PCI Categorical was first launched in 2003, and at the moment’s 6.0 launch primarily marks the third main revision of the know-how. Whereas PCIe 4.0 and 5.0 had been “merely” extensions to earlier signaling strategies – particularly, persevering with to make use of PCIe 3.0’s 128b/130b signaling with NRZ – PCIe 6.0 undertakes a extra vital overhaul, arguably the most important within the historical past of the usual.

As a way to pull of one other bandwidth doubling, the PCI-SIG has upended the signaling know-how totally, shifting from the Non-Return-to-Zero (NRZ) tech used for the reason that starting, and to Pulse-Amplitude Modulation 4 (PAM4).

As we wrote on the time that growth on PCIe 6.0 was first introduced:

PAM4 itself is just not a brand new know-how, however up till now it’s been the area of ultra-high-end networking requirements like 200G Ethernet, the place the quantity of house accessible for extra bodily channels is much more restricted. In consequence, the business already has a number of years of expertise working with the signaling customary, and with their very own bandwidth wants persevering with to develop, the PCI-SIG has determined to carry it contained in the chassis by basing the subsequent era of PCIe upon it.

The tradeoff for utilizing PAM4 is in fact value. Even with its larger bandwidth per Hz, PAM4 presently prices extra to implement at just about each stage, from the PHY to the bodily layer. Which is why it hasn’t taken the world by storm, and why NRZ continues for use elsewhere. The sheer mass deployment scale of PCIe will in fact assist rather a lot right here – economies of scale nonetheless depend for lots – however it is going to be fascinating to see the place issues stand in a number of years as soon as PCIe 6.0 is in the course of ramping up.

In the meantime, not not like the MLC NAND in my earlier analogy, due to the extra sign states a PAM4 sign itself is extra fragile than a NRZ sign. And which means that together with PAM4, for the primary time in PCIe’s historical past the usual can also be getting Ahead Error Correction (FEC). Residing as much as its identify, Ahead Error Correction is a way of correcting sign errors in a hyperlink by supplying a continuing stream of error correction knowledge, and it’s already generally utilized in conditions the place knowledge integrity is vital and there’s no time for a retransmission (comparable to DisplayPort 1.4 w/DSC). Whereas FEC hasn’t been essential for PCIe till now, PAM4’s fragility goes to vary that. The inclusion of FEC shouldn’t make a noticeable distinction to end-users, however for the PCI-SIG it’s one other design requirement to deal with. Specifically, the group must guarantee that their FEC implementation is low-latency whereas nonetheless being appropriately strong, as PCIe customers received’t desire a vital improve in PCIe’s latency.

It’s price noting that FEC can also be being paired with Cyclic Redundancy Checking (CRC) as a last layer of protection towards bit errors. Packets that, even after FEC nonetheless fail a CRC – and thus are nonetheless corrupt – will set off a full retransmission of the packet.

The upshot of the swap to PAM4 then is that by rising the quantity of knowledge transmitted with out rising the frequency, the sign loss necessities received’t go up. PCIe 6.0 could have the identical 36dB loss as PCIe 5.0, which means that whereas hint lengths aren’t formally outlined by the usual, a PCIe 6.0 hyperlink ought to have the ability to attain simply so far as a PCIe 5.0 hyperlink. Which, coming from PCIe 5.0, is little doubt a reduction to distributors and engineers alike.

Alongside PAM4 and FEC, the ultimate main technological addition to PCIe 6.0 is its FLow management unIT (FLIT) encoding technique. To not be confused with PAM4, which is on the bodily layer, FLIT encoding is employed on the logical stage to interrupt up knowledge into fixed-size packets. It’s by shifting the logical layer to fastened measurement packets that PCIe 6.0 is ready to implement FEC and different error correction strategies, as these strategies require mentioned fixed-size packets. FLIT encoding itself is just not a brand new know-how, however like PAM4, is actually being borrowed from the realm of high-speed networking, the place it’s already used. And, in response to the PCI-SIG, it’s probably the most essential items of the specification, because it’s the important thing piece to enabling (continued) low-latency operation of PCIe with FEC, in addition to permitting for very minimal overhead. All advised, PCI-SIG considers PCIe 6.0 encoding to be a 1b/1b encoding technique, as there’s no overhead within the knowledge encoding itself (there may be nevertheless overhead within the type of further FEC/CRC packets).

Because it’s extra of an enabling piece than a function of the specification, FLIT encoding ought to be pretty invisible to customers. Nevertheless, it’s essential to notice that the PCI-SIG thought of it essential/helpful sufficient that FLIT encoding can also be being backported in a way to decrease hyperlink charges; as soon as FLIT is enabled on a hyperlink, a hyperlink will stay in FLIT mode always, even when the hyperlink fee is negotiated down. So, for instance, if a PCIe 6.0 graphics card had been to drop from a 64 GT/s (PCIe 6.0) fee to a 2.5GT/s (PCIe 1.x) fee to save lots of energy at idle, the hyperlink itself will nonetheless be working in FLIT mode, fairly than going again to a full PCIe 1.x type hyperlink. This each simplifies the design of the spec (not having to renegotiate connections past the hyperlink fee) and permits all hyperlink charges to profit from the low latency and low overhead of FLIT.

As at all times, PCIe 6.0 is backwards appropriate with earlier specs; so older gadgets will work in newer hosts, and newer gadgets will work in older hosts. As nicely, the present types of connectors stay supported, together with the ever present PCIe card edge connector. So whereas assist for the specification will have to be constructed into newer generations of gadgets, it ought to be a comparatively simple transition, identical to earlier generations of the know-how.

Sadly, the PCI-SIG hasn’t been in a position to give us a lot in the way in which of steering on what this implies for implementations, significantly in client techniques – the group simply makes the usual, it’s as much as {hardware} distributors to implement it. As a result of the swap to PAM4 signifies that the quantity of sign loss for a given hint size hasn’t gone up, conceptually, putting PCIe 6.0 slots ought to be about as versatile as putting PCIe 5.0 slots. That mentioned, we’re going to have to attend and see what AMD and Intel devise over the subsequent few years. Having the ability to do one thing, and with the ability to do it on a client {hardware} funds aren’t at all times the identical factor.

Wrapping issues up, with the PCIe 6.0 specification lastly accomplished, the PCI-SIG tells us that, primarily based on earlier adoption timelines, we must always begin seeing PCIe 6.0 compliant {hardware} hit the market in 12-18 months. In observe which means that we must always see the primary server gear subsequent 12 months, after which maybe one other 12 months or two for client gear.

Supply By https://www.anandtech.com/present/17203/pcie-60-specification-finalized-x16-slots-to-reach-128gbps